摘要:主要介绍以FPGA为硬件平台的下位机与计算机(上位机)进行串行通信,将串口功能集成到单片FPGA内,运行中波特率可调,经过适当的倍、分频实现了零误差的波特率发生器,提高了数据传输的可靠性。上位机上编写VB程序负责主设备的发送命令并接收显示来自FPGA回发的数据,实验结果表明通信可行,可靠性高。

串行通信广泛应用于数字通信和工业控制领域,传统的专用串口通信芯片接口复杂,体积较大,随着微电子技术的发展,FPGA的等效门数迅速增加,可以完全将串口功能集成在单片FPGA内,减少了外围电路的体积,降低了设计的复杂性,同时也提高通信的可靠性。

1 串行通信的原理

串行通信是指通信的发送和接收方之间数据信息的传输是在单根数据线上完成,以每次一个二进制的0或1为最小单位逐位进行传输,本文采用异步的全双工通信方式,数据传输是以字符为单位,如图1所示为异步通信的帧格式。

其中,一帧数据包括起始位、数据位、校验位和停止位。线路空闲状态下,发送和接收端均保持高电平;通信开始时,通信一方发送一个起始位(低电平),表示通信的开始,紧接着发送有效的数据位,通常约定的数据位有5,6,7或者8位,根据用户需要进行设定,然后发送校验位,这里选用偶校验,最后发送停止位,可以是1,1.5或2位不等,用户自行约定即可。本文选用8位数据位、偶校验、1位停止位,可以实现所有字符的收、发。

串行通信传送数据是按位顺序进行,最少只需要一根传输线即可完成,要实现全双工的通信共需要2根数据线和1根接地线即可,通信双方可以在同一时刻进行发送和接收的操作。本文采用的是RS232C串行接口标准,是目前PC机与通信工业中应用最广泛的一种串行接口。但计算机的串口是用正负电压来表示逻辑状态,与FPGA电路板上以高低电平表示的逻辑状态的标准不同。因此,为了能够同计算机进行通信,必须在两者之间进行电平的逻辑关系转换,本文采用集成电路芯片MAX232来完成两种电平的双向转换。如图2所示。

2 FPGA收发模块的实现

要使FPGA具有数据的收发功能,则收、发两模块必不可少,与此相关联的还需要收、发的时钟即波特率产生器,收发监视器以及输入/输出缓冲器。本文采用先进先出存储器(First in First Out,FIFO)作为收发数据的双向缓冲器。如图3所示为FPGA实现串口数据收发的整体框图。收、发模块原理基本相同,只是发送区的发送控制信号受FIFO的读空信号控制。本文重点介绍接收数据的过程。

2.1 接收区模块

接收区模块负责数据的串行接收并转换为并行数据,然后送入FIFO存储器以备后用。它主要由起始位检测模块、波特率可调的波特率产生模块和接收模块组成。

(1)波特率产生器

串行通信的传输受到通信双方配备性能及通信线路的特性所左右,收、发双方必须约定相同的速率进行串行通信,即收、发双方采用相同的数据传输速率,就仪器和工业场合来说,最常见的数据传输率有4800b/s,9600b/s等,现在个人计算机提供的串行端口的数据传输率甚至达到115200b/s。若传输距离较近且设备提供的情况下使用最高的数据传输率。本文所列的波特率产生器灵活多变,可以根据实际条件选择不同的数据传输率。设计中添加了一位拨码开关(Key),故运行中可以在两种波特率中进行选择。这里选用了4800b/s,9600b/s两种常见的数据传输速率,当Key为低电平时选择4800b/s,为高电平时选择9600b/s。当然,以此类推运用二个拨码开关即可实现4种波特率的互调等。

本文采用50MHz时钟源,所以要得到4800b/s和9600b/s的传输率分别需要进行5208次和31250次分频。分频参数如表1所示。从表中第1,3两行可以看出如果只用系统提供的50MHz时钟源,得到的两种波特率均存在误差0.0064%。可以灵活运用倍、分频原理进一步减小误差。从表中第2,4行可以看出,当时钟提高到150MHz时,两种数据传输率的分频系数刚好能取到整数,也就是说实际可以得到理想的数据传输速率。但从50~150MHz需要经过3倍频,如果硬件允许的情况下可以采用3倍频,能够使传输可靠性更高,本文采用的就是此方法。由于设计中采用的硬件是Altera公司CycloneⅡ系列FPGA,拥有2个锁相环,可以进行灵活的倍、分频,所以能够满足3倍频的要求。

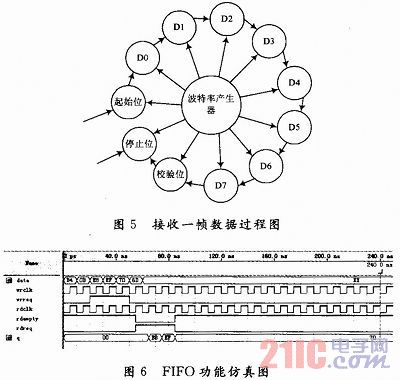

(2)起始位检测器与接收模块为使得程序清晰,这两个模块用状态机进行实现,如图4所示。系统复位后进入空闲状态,空闲状态时起始位检测器不断检测接收管脚(RxD)上的信号,当检测器检测到低电平到来后,状态转移到接收状态,接收模块便按照约定的波特率开始接收数据,如图5所示。与此同时建立相应的接收位计数器,当计数满11后(1位起始位、8位数据位、1位校验位和1位停止位),状态又反跳到空闲状态,如此循环下去,不断接收来自上位机发送的数据。同时为使得接收的数据更加稳定,设计时在接收模块接收时采用中间采样的方法,如选择9600b/s的数据传输率,则在半分频系数即7812时采样数据。

2.2 存储器

接收区接收一帧数据后将数据位存入临时寄存器中,为防止新数据对其覆盖,故在此添加一个存储器,每接收1B数据后将临时寄存器中的数据写入FIFO中。这里采用了异步的先进先出存储器,实现简单,直接调用相应的IP核。模块中选择8位数据位,存储深度可根据器件特性灵活选择,这里选则4个字的存储深度。本文只是为了测试通信的正确性,且收、发速率相同,所以4个字的存储深度能够满足要求。FIFO外部管脚主要包括读/写时钟,数据输入/输出以及读空信号,实验中读空信号rdempty送到发送检测器输入端用来控制FIFO对外的数据输出。如图6所示为其在QuartusⅡ下的功能仿真图。wrclk和rdclk分别为写时钟和读时钟,当写信号wrreq有效时将外部数据data写入FIFO,本设计中读信号rdreq由读空信号rdempty控制,当读空信号rdempty为低电平(FIFO非空)时读信号rdreq有效,此时将FIFO中的数据读出并通过q端输出,读空FIFO后读空信号rdreq跳到高电平。

3 基于VB的上位机程序设计

为了验证PC机与FPGA硬件的通信,上位机采用Visual Basic开发Windows下的测控软件。就串口而言,利用VB开发了串口通信程序有两种方法:一是使用MSComm串口控件;二是调用Windows API函数。本文采用了前者,与调用API函数相比,MSComm控件实现更加方便、快捷。

MSComm是VB对使用串口通信的用户定制的控件,它提供了一系列标准通信属性和方法,简单编写相关程序便可实现串行端口的连接。主要用到的属性如表2所示。

为验证FPGA与PC的通信,需要编写发送和接收程序,为简化程序,部分属性直接在注册表中设定。如InPutMode设定为1即二进制方式读取数据;由于程序接收部分使用OnComm事件,所以这里把SThreshold属性设定为1,而RThreshold属性设定为发送数据的字节数,即接收缓冲区接收到全部字节数后MSComm控件触发OnComm事件,执行相应的接收程序。InBufferSize和OutBufferSize均设置为1024即1KB缓冲空间。

如下是发送和接收子程序:

4 实验验证

实验过程中串行数据的收、发等功能在Altera公司的CycloneⅡ系列EP2C5芯片下实现,在VB 6.0中编写相应的FPGA与PC通信的调试窗口,如图7所示为数据传输率9600b/s的实验结果。

打开应用程序,设置好通信端口、约定的通信速率、数据位等,在相应的输入框输入“FPGA与PC通信成功!”字符,点击5次发送,从显示区可以看到理想的结果,实验结果表明FPGA与PC通信可靠。

5 结语

本文实现了计算机与FPGA的串口通信,结合上位机的VB程序验证了通信的正确性。设计过程中FIFO部分运用了IP核使得程序更加简洁,且外加了一位拨码开关,实现了运行过程中两种波特率的灵活选择。实际运用中可以再相应地增加拨码开关实现多波特率多数据位等的互调,不必为了适应不同的通信标准而重新编写代码、重新配置。FPGA部分的程序在QuartusⅡ9.1环境下编辑、调试,综合结果显示共占用FPGA的144个逻辑单元、81个专用逻辑寄存器、32位存储器和1个锁相环,相比百万门大规模FPGA占用资源很少,可以作为IP核灵活移植到其他工程中实现与PC的串行通信,为今后的设计开发提供参考。

作者:蔡德胜 方寿海 南京工业大学电子与信息工程学院 来源:《现代电子技术》2011年第19期

相关专题:

相关专题: