еЊвЊЃКдкбаОПЪ§ПиеёЕДЦїNCOЙЄзїдРэЕФЛљДЁЩЯЃЌЭЈЙ§ЗжЮіЖдБШМИжжВЛЭЌЕФNCOЩшМЦЗНЗЈЃЌВЩгУСЫЫуЗЈМђЕЅЁЂНкЪЁзЪдДЕФЛљгкROMВщевБэЕФЩшМЦЗНЗЈЁЃеыЖде§НЛЪ§ПиеёЕДЦїNCOЕФжївЊВПМўе§грЯвДцДЂБэЁЂПЩБфФЃМЦЪ§ЦїНјааСЫЫуЗЈЩшМЦКЭЕчТЗЩшМЦЃЌВЂдкAlteraЙЋЫОЕФFPGAЩЯНјааСЫбщжЄЃЌВЈаЮЗТецНсЙћБэУїСЫЕчТЗЩшМЦЕФе§ШЗадЁЃВЩгУВщевБэЕФЗНЗЈПЩвдгааЇЬсИпЯЕЭГЙІФмЕФПЩРЉеЙадКЭЯЕЭГЕФПЩМЏГЩадЃЌЪЙЕУNCOЙІФмФЃПщПЩвдЭЈЙ§ХфжУДцДЂБэЁЂЦЕТЪПижЦзжРДТњзуЖржжгІгУГЁКЯЯТЕФNCOЩшМЦашвЊЃЌПЩвдЙуЗКЕигІгУгкИїжжЯжДњЭЈаХЯЕЭГжаЁЃ

ЫцзХЪ§зжЭЈаХММЪѕЕФЗЩЫйЗЂеЙЃЌШэМўЮоЯпЕчЕФгІгУгњМгЕФЙуЗКЃЌЖјгАЯьШэМўЮоЯпЕчадФмЕФЙиМќЦїМўЪ§ПиеёЕДЦїNCO(Numerical CONtrolled Oscillator)ЕФЩшМЦжСЙиживЊЃЛNCOЕФЩшМЦВЩгУжБНгЪ§зжЦЕТЪКЯГЩ(DDS)ММЪѕЃЛ1971Фъ3дТУРЙњбЇепJ.TierncyЁЂC.M.RaderКЭB.GoldЪзДЮЬсГіСЫжБНгЪ§зжЦЕТЪКЯГЩ(DDS)ММЪѕЁЃетЪЧвЛжжДгЯрЮЛИХФюГіЗЂжБНгКЯГЩЫљашвЊЕФВЈаЮЕФаТЕФШЋЪ§зжЦЕТЪКЯГЩММЪѕЁЃЭЌДЋЭГЕФЦЕТЪКЯГЩММЪѕЯрБШЃЌDDSММЪѕОпгаЦЕТЪОЋЖШИпЁЂзЊЛЛЪБМфЖЬЁЂЦЕЦзДПЖШИпвдМАЦЕТЪЯрЮЛвзБрГЬЁЂЪфГіЕФЦЕТЪЮШЖЈЖШгыЯЕЭГЕФЪБжгЮШЖЈЖШЯрЭЌЕШвЛЯЕСагХЕуЃЌЙуЗКгІгУгкЯжДњИїжжЭЈаХЯЕЭГжаЃЌАќРЈЪ§зжЩЯЯТБфЦЕЁЂжаЦЕБфЛЛЁЂЦЕТЪКЯГЩвдМАРЉЦЕЯЕЭГКЭИїжжЦЕТЪЯрЮЛЪ§зжЕїжЦНтЕїЯЕЭГжаЁЃ

дкШэМўЮоЯпЕчМАЭЈаХСьгђЃЌОГЃЪЙгУе§НЛЕФЪ§зжаХКХЃЛеыЖдДЫРргІгУЃЌБОЮФИјГіСЫвЛжжЛљгкFPGAЕФе§НЛNCOЩшМЦЗНЗЈЃЌПЩвдЪЕЯже§НЛЕФЁЂСЌајЯрЮЛЁЂИпадФмЁЂИпОЋЖШЁЂПЩжиРћгУЕФЪ§ПиеёЕДЦїЃЌЪЪКЯгкЖржжгІгУГЁОАЕФЦЌЩЯЯЕЭГЕФЩшМЦЁЃ

1 NCOЪЕЯждРэ

жБНгЪ§зжЦЕТЪКЯГЩ(DDS)ММЪѕЪЧвЛжжШЋЪ§зжММЪѕЃЌЭЌДЋЭГЕФЦЕТЪКЯГЩММЪѕЯрБШЃЌDDSММЪѕОпгаЖрЯюгХЕуЃКЦЕТЪЧаЛЛЪБМфЖЬЁЂЦЕТЪЗжБцТЪИпЁЂЯрЮЛБфЛЏСЌајЁЂШнвзЪЕЯжЖдЪфГіаХКХЕФЖржжЕїжЦЕШЁЃ

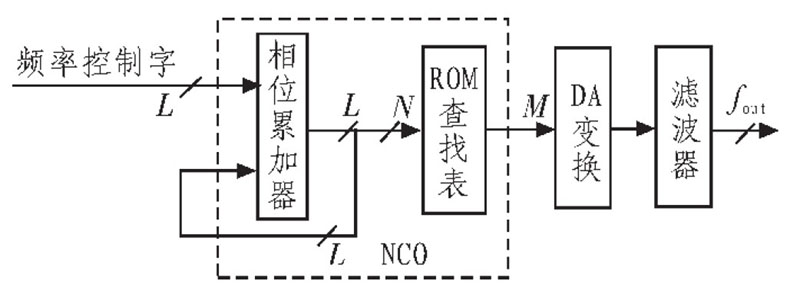

DDSЕФдРэПђЭМШчЭМ1ЫљЪОЃЌЦфЪЕжЪЪЧвдЛљзМЦЕТЪдД(ЯЕЭГЪБжг)ЖдЯрЮЛНјааЕШМфИєЕФВЩбљЁЃгЩЭМ1ПЩМћЃЌDDSгЩЯрЮЛРлМгЦїКЭВЈаЮДцДЂЦї(ROMВщбЏБэ)ЙЙГЩЕФЪ§ПиеёЕДЦї(NCO)ЁЂЪ§ФЃзЊЛЛЦї(DAC)вдМАЕЭЭЈТЫВЈЦї(LPF)3ВПЗжзщГЩЁЃЖјDDSЕФКЫаФЪЧNCOЕФЩшМЦгыЪЕЯжЃЌNCOвЛАуЪЧгЩЯрЮЛРлМгЦїКЭе§грЯвВщевБэСНВПЗжзщГЩЃЌЦфжаЯрЮЛРлМгЦїЕФЩшМЦНЯМђЕЅЃЌЙЪЩшМЦNCOЕФЙиМќЪЧЩшМЦе§ЁЂгрЯвКЏЪ§ЗЂЩњЦїЁЃ

ЪЕЯжКЏЪ§ЗЂЩњЦїЕФЗНЗЈЮЊВщБэЗЈ(LUT)ЃЌЖдгквЛИіЯрЮЛЮЛЪ§ЮЊLЃЌЪфГіаХКХЗљЖШЮЛЪ§ЮЊMЕФNCOЃЌЫљашВщевБэЕФДѓаЁЮЊM×2LЁЃ

ЭМ1 DDSЛљБОдРэПђЭМ

дкУПвЛИіЪБжгжмЦкЃЌLЮЛЯрЮЛРлМгЦїгыЦфЗДРЁжЕНјааРлМгЃЌЦфНсЙћЕФИпNЮЛзїЮЊROMВщбЏБэЕФЕижЗЃЌШЛКѓДгROMжаЖСГіЯргІЕФЗљЖШжЕЫЭЕНDACЁЃЕЭЭЈТЫВЈЦїLPFгУгкТЫГ§DACЪфГіжаЕФИпДЮаГВЈЁЃвђДЫЭЈЙ§ИФБфЦЕТЪПижЦзжKОЭПЩвдИФБфЪфГіЦЕТЪfoutЁЃШнвзЕУЕНЪфГіЦЕТЪfoutгыЦЕТЪПижЦзжK ЕФЙиЯЕЮЊЃКfout=Kfc/2LЃЌЦфжаfcЮЊЯрЮЛРлМгЦїЕФЪБжгЦЕТЪЃЌLЮЊЯрЮЛРлМгЦїЕФЮЛЪ§ЁЃЖЈвхЕБK=1ЮЊЯЕЭГЦЕТЪЗжБцТЪЃЌМДf=fc/2LЁЃ

2 NCOМИжжГЃМћЩшМЦЗНЗЈ

ГЃМћЕФNCOЪЕЯжЕФЗНЗЈФПЧАжївЊгаМЦЫуЗЈЁЂCORDIC(Coordinated RotATIon DigitalComputer)ЫуЗЈКЭВщБэЗЈЕШЁЃ

МЦЫуЗЈЪЧвЛжжвдШэМўБрГЬЕФЗНЪНЭЈЙ§ЪЕЪБМЦЫуВњЩње§ЯвВЈбљБОЃЌИУЗНЗЈКФЪБЖрЧвжЛФмВњЩњЦЕТЪЯрЖдНЯЕЭЕФе§ЯвВЈЃЌЖјашвЊВњЩњИпЫйЕФе§НЛаХКХЪБЃЌгУДЫЗНЗЈВЛФмКмКУЕФТњзувЊЧѓЁЃ

CORDICЫуЗЈМДзјБъа§зЊЪ§зжМЦЫуЗНЗЈЃЌЦфЛљБОЫМЯыЪЧгУвЛЯЕСаЙЬЖЈНЧЖШЕФВЛЖЯЦЋАкБЦНќЫљаша§зЊЕФНЧЖШЃЌЪЕЯжАќРЈГЫГ§ЁЂЦНЗНИљЁЂШ§НЧКЏЪ§ЁЂЯђСПа§зЊ(МДИДЪ§ГЫЗЈ)вдМАжИЪ§дЫЫуЃЌИУЫуЗЈЭљЭљашвЊЭЈЙ§ГЫЗЈЦїКЭВщевБэВХФмЪЕЯжЖржжГЌдНКЏЪ§ЕФМЦЫуЃЌетЛсЕМжТгВМўЕчТЗЪЕЯжИДдгЁЂдЫЫуЫйЖШНЕЕЭЃЌДЫЭтЫќФмЙЛМЦЫуЕФНЧЖШЗЖЮЇвВгаЯоЃЌЙЪCORDICЫуЗЈдкЪЕМЪЪЙгУЪБгаНЯДѓЕФЯожЦЬѕМўЁЃ

дкЪЕМЪгІгУжавЛАуВЩгУзюгааЇЁЂзюМђЕЅЕФВщБэЗЈЃЌМДЪТЯШИљОнИїИіNCOе§ЯвВЈЯрЮЛМЦЫуКУЯрЮЛЕФе§ЯвжЕЃЌВЂвдЯрЮЛНЧЖШзїЮЊЕижЗАбИУЯрЮЛЕФе§ЯвжЕЪ§ОнДцДЂдкБэжаЃЌШЛКѓЭЈЙ§ЯрЮЛРлМгВњЩњЕижЗаХЯЂЖСШЁЕБЧАЪБПЬЕФЯрЮЛжЕдкБэжаЖдгІЕФе§ЯвжЕЃЌДгЖјВњЩњЫљашЦЕТЪЕФе§ЯвВЈЃЛЭЌЪБгЩгке§грЯвВЈаЮЕФЖдГЦадЃЌжЛашвЊДцДЂВПЗжЪ§ОнМДПЩЭъГЩШЋЯрЮЛЕФЪ§жЕЪфГіЁЃетжжЪЕЯжЗНЗЈЃЌЩшМЦМђЕЅЁЂдЫЫуЫйЖШНЯИпЃЌПЩвдКмКУЕФТњзудкЪ§зжБфЦЕЁЂРЉЦЕЁЂЕїжЦНтЕїЕШЖржжГЁКЯЕФвЊЧѓЁЃ

3 е§НЛNCOЕФВщевБэЪЕЯжЗНЗЈ

ЛљгкFPGAЕФе§НЛNCOЩшМЦдРэПђЭМШчЭМ2ЫљЪОЃЌжївЊгЩ3ВПЗжзщГЩЃКПЩБфФЃМЦЪ§ЦїЁЂе§грЯвВщевБэКЭЪфГіЕЅдЊ3ИіФЃПщзщГЩЁЃ

ЭМ2 NCOЕФЩшМЦдРэПђЭМ

ЯТУцвдЪфШыЕФЦЕТЪПижЦзжЮЊ1200HzЮЊР§НјааЩшМЦЁЃ

Fre_sampleЃЌБэЪОЯЕЭГВЩгУЪБжгЃЛFre_cnt_wordБэЪОЦЕТЪПижЦзжЁЃ

1)ПЩБфФЃМЦЪ§ЦїЕФЩшМЦ

ПЩБфФЃМЦЪ§ЦїЪЧИљОнЦЕТЪПижЦзжЃЌМЦЫуГіе§грЯвБэЕФВщБэЫљашЕФЕижЗЃЛЭЌЪБвЊБЃжЄВњЩњЕФе§грЯвВЈЕФЯрЮЛБЃГжСЌај(гааЉгІгУГЁКЯГЃГЃвЊЧѓЪфГіЕФЯрЮЛСЌај)ЃЌМДжУгкЯргІЕФгрЪ§жЕЁЃдкЕк1ИіЙЄзїЪБжгжмЦкЖСШыЦЕТЪПижЦзжЃЌЕк2ИіЙЄзїЪБжгжмЦкФкМЦЫуГіmod(Fre_sampleЃЌFre_cnt_word)зїЮЊЯрЮЛПижЦзжЃЌЕк3ИіЙЄзїЪБжгжмЦкФкВПМЦЪ§ЦїИДЮЛжУШыЯрЮЛПижЦзжЃЌЕк4ИіЪБжгжмЦкПЊЪМвдЦЕТЪПижЦзжЮЊВНГЄЃЌЯрЮЛПижЦзжЮЊГѕЪМжЕНјааМЦЪ§ЪфГіЁЃ

2)е§грЯвВщевБэЕФЩшМЦ

е§грЯвВщевБэЪЧИљОнПЩБфФЃМЦЪ§ЦїЕФЪфГіВщБэЕУЕНЯргІдиЦЕВЈаЮЕФЪфГіЁЃ

ЛљгкFPGAЕФNCOЩшМЦЕФвЛИіЙиМќОЭЪЧВЈаЮДцДЂЦїROMЯрЮЛРлМгЦїЕФЪфГіЕижЗзїЮЊROMЕФЕижЗЪфШыЃЌОВщБэКЭдЫЫуКѓЃЌROMЪфГіе§грЯвВЈаЮЕФСПЛЏЪ§ОнЃЛЩшМЦжажївЊЪЧвЊНкЪЁДцДЂЦїзЪдДЕФПЊЯњЃЌМДМѕаЁROMДцДЂБэЕФПеМфЃЛгЩгкДцДЂБэЕФГпДчЫцзХЕижЗЮЛЪ§ЛђЪ§ОнЮЛЪ§ЕФдіМгГЪЯжжИЪ§МЖЕндіЙиЯЕЃЌЫљвддкТњзуЦЕТЪЗжБцТЪЁЂаХКХадФмЕФЧАЬсЯТЃЌжївЊПМТЧНЯаЁROMДцДЂБэЕФПЊЯњЃЛдкЪЕМЪЕФгІгУжаЃЌПЩвдГфЗжРћгУе§грЯваХКХдквЛИіжмЦкФкЕФЖдГЦадРДМѕЩйROMДцДЂБэЕФПЊЯњЃЌР§Шче§ЯваХКХЃЌдквЛИіжмЦкФкЖдгкXжсЪЧЖдГЦЕФЃЌЛљгкДЫПЩвдНЋROMДцДЂБэМѕЩйжСдРДЕФ1/2ЃЌдйРћгУАыжмЦкФкЕФзѓгвЖдГЦадЃЌгжПЩвдНЋROMДцДЂБэМѕЩйжСдРДЕФ1/2ЃЌвђДЫЭЈЙ§вЛИіе§ЯвВщевБэЕФЧА1/4жмЦкОЭПЩвдБфЛЛЕУЕНећИіе§ЯвВЈжмЦкВщевБэЃЌетбљОЭНкЪЁСЫ3/4ЕФДцДЂЦїзЪдДЁЃ

е§грЯвБэЕФОпЬхЩшМЦЫМЯыШчЯТЃКШЁЦЕТЪЗжБцТЪЮЊdf=1HzЃЛМйЩшЦЕТЪПижЦзжЮЊ1200HzЕФЦЕТЪзѓгвЃЌЯжПМТЧЖд1200HzЕФе§грЯвВЈаЮУПвЛИіжмЦкВЩ8ИібљЕуЃЌдђПЩЕУВЩбљТЪЮЊfs=1200×8=9600HzЁЃЩшЖдгкУПвЛИібљЕужЕШЁ8bitСПЛЏЃЌдђУПИіБэИёЙВашДцДЂ9.6kBЃЛ(ШчЙћПМТЧЕНе§ЁЂгрЯваХКХЕФЖдГЦадЃЌЩшМЦЪБПЩгХЛЏЮЊЩЯУПИіБэИёДцДЂ1/4ИіВЈаЮМДПЩЃЌМДУПИіБэИёжЛашДцДЂ2.4kBЃЛ)ЪЙгУЪБЪЧгУВНГЄSTepРДЕїНкЪфГіЦЕТЪЃЌЭЌЪББЃжЄЪфГіЕФе§грЯвВЈЕФЯрЮЛСЌајЁЃШчЙћУПИє0бљЕуШЁ1ЃЌМДstep=1ЃЌЪфГіЦЕТЪЮЊ1HzЃЛУПИє1ЕуШЁ1ЃЌМДstep=2ЃЌЪфГіЦЕТЪЮЊ2HzЃЛ……ЃЛУПИє1199ЕуШЁ1ЃЌstep=1200ЃЌЪфГіЦЕТЪЮЊ1200HzЁЃ

3)е§грЯвБэЕФзАди

ВЩгУQuartusШэМўжаЕФЁЃmif ЮФМўИёЪНПЩвдЗНБуЕФЭъГЩДцДЂБэЕФзАдиЃЛЭЌЪБЖдгкзАдиЮФМўЕФЩњГЩПЩвдЪЙгУmatlabЪфГіЁЃmifЕФЮФМўИёЪНКмЗНБуЕФЩњГЩЃЛШчЯТЮФжаИјГіСЫЮЛПэЮЊ8bitЃЌЩюЖШЮЊ9600ЃЌЕижЗЮЊЮоЗћКХЪ§ЃЌЪ§ОнЮЊЪЎНјжЦЪ§ЕФ9600ИіЕЅдЊЕФmifЮФМўЃЌдкГѕЪМЛЏRAMЪБЃЌАДееQuartusШэМўЕФв§ЕМжБНгХфжУМДПЩЁЃ

WIDTH=8ЃЛ

DEPTH=9600ЃЛ

ADDRESS_RADIX=UNSЃЛ

DATA_RADIX=DECЃЛ

CONTENT BEGIN

0 : 0ЃЛ

1 : 2ЃЛ

2 : 10ЃЛ

3 : 30ЃЛ

4 : 50ЃЛ

5 : 50ЃЛ

6 : 10ЃЛ

7 : 100ЃЛ

……

9598 : 0ЃЛ

9599 : 0ЃЛ

END

4 ЩшМЦЪЕЯжМАЦфЗТецВЈаЮ

БОДЮЩшМЦВЩгУадМлБШНЯИпЕФALTERAЙЋЫОЕФSTRATIXаОЦЌНјааЩшМЦЗТецЃЌИУЯЕСааОЦЌЪЧЛљгк1.5VЙЄзїЕчбЙЁЂ0.13μmШЋЭВМЯпSRAMЙЄвеЕФFPGAаОЦЌЁЃДЫЯЕСааОЦЌгЕгазюЖр114140ИіТпМЕЅдЊ(Les)КЭзюЖр10MbitsЕФФкВПRAMЁЃИУЯЕСааОЦЌжЇГжЖржжI/OБъзМЃЌЬсЙЉСЫзюЖрПЩДя12ИіЕФгУгкДІРэИДдгЪБжгаХКХЕФЫјЯрЛЗ(PLLs)ЁЃЭЌЪБЃЌSTRATIXЯЕСааОЦЌЬсЙЉСЫзюЖрПЩДя28ИіЕФЪ§зжаХКХДІРэЕЅдЊ(DSP)ЃЌЫќУЧгЩзмЙВ224ИіФкжУгВМўГЫЗЈЦї(9ЮЛГЫ9ЮЛ)зщГЩЃЌРћгУЫќУЧПЩвдгааЇЕиЪЕЯжР§ШчПьЫйИЕСЂвЖБфЛЛ(FFT)ЁЂгаЯоГхЛїЯьгІ(FIR)ТЫВЈЦїЁЂЮоЯоГхЛїЯьгІ(IIR)ТЫВЈЦїЕШИпадФмЕФЪ§зжаХКХДІРэЕЅдЊЛђепГЫЗЈЦїЁЃ

ЭМ3 NCOФЃПщЕФжївЊЖЫПкЖЈвх

2)QuartusЗТецЪфГіВЈаЮЃЌШчЭМ4ЫљЪОЁЃ

ЭМ4 NCOЕФЗТецЪфГіВЈаЮ

ДЫЗТецВЈаЮЮЊ3ИіЦЕЕуЕФNCOЪфГіВЈаЮЃЌгУmatlabЛцГіЪфГіЕФдиВЈЕФВЈаЮШчЭМ5ЫљЪОЁЃ

ЭМ5 ЪфГідиВЈЕФВЈаЮ

гЩЩЯУцЕФЗТецНсЙћПЩвдПДГіЃЌNCOе§ШЗЪфГіСЫ3ИіЦЕЕуЕФЗТецВЈаЮЃЛЭЌЪБЭЈЙ§ЪЕМЪЕФFPGAгВМўВтЪдКЭбщжЄЃЌИУЩшМЦДяЕНСЫЫљвЊЧѓЕФадФмжИБъЁЃ

5 зЪдДеМгУЧщПі

ЪЙгУAlteraЙЋЫОЕФSTRATIXаОЦЌНјааБрвыЁЂзлКЯЃЌЫљЕУЕФзЪдДеМгУНсЙћШчЭМ6ЫљЪОЁЃ

ЭМ6 NCOзЪдДеМгУЧщПі

6 НсЪјгя

БОЮФИјГіСЫвЛжжЛљгкFPGAЕФе§НЛNCOЕФЩшМЦЗНЗЈЃЌдкЪЕМЪгІгУЙ§ГЬжаПЩВЮПМИјГіЕФЩшМЦЪЕР§ЃЌЭЈЙ§ИФБфЦЕТЪПижЦзжЁЂЯЕЭГВЩбљЦЕТЪЁЂДцДЂе§грЯвВщевБэЕФЩюЖШКЭДцДЂБэЕФЮЛПэЃЌМДПЩЕУЕНВЛЭЌЪфШыЦЕТЪЗЖЮЇЕФNCOЃЛЭЌЪБШчЙћЩцМАашвЊЕФОЋЖШМАЦЕТЪНЯИпЃЌвВПЩВЩгУЭтжУЕФДцДЂЦїЃЌШчFLASHЃЌSRAMЕШгыFPGAХфКЯЪЙгУЃЌНЯДѓЕФРЉеЙДцДЂБэЕФЩюЖШКЭЮЛПэЃЌПЩзюжеДяЕНЩшМЦЕФвЊЧѓЁЃ

зїепЃКеХАЂФў едЦМ ЮїАВгЪЕчбЇдКЕчзгЙЄГЬбЇдК РДдДЃКЁЖЕчзгЩшМЦЙЄГЬЁЗ2011Фъ17Цк

ЮвЭЦМіДѓМвЖС

ЧсЫЩВЮгы

VS

БэДяСЂГЁ

етЪЧРЌЛјЮФеТ

ЯрЙизЈЬтЃК

ЯрЙизЈЬтЃК